|

1.開発の背景

地球温暖化対策としてCO2削減が求められる一方、都市化、エネルギー電化、AI拡大等により電力需要の世界的な増大が見込まれている。電力変換効率を高めるパワー半導体の重要性は高く、Siの物性限界を超えるSiCパワー半導体が期待されているが、SiCエピタキシャルウェハー(エピウェハー)*1)の高品質化・低コスト化が社会実装の障壁であった。そこで本開発では、高品質エピ膜の高生産性製造技術の確立に取り組んだ。

*1) SiC基板の上にSiCエピ膜を成膜したもの

2.開発技術の概要

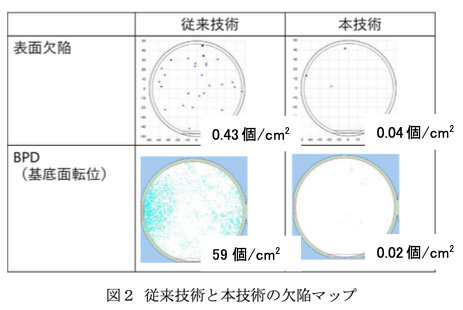

従来装置でのエピ膜の表面欠陥の主要因は、成膜中に装置内部に生成するデポ(副生成物)の基板上へのパーティクルとして落下であったが、本開発ではその現象を根本的に抑制する装置設計を通じて低欠陥化を実現した。併せて、基板から伝播する内在欠陥である基底面転位(BPD)を顕著に低減する界面制御プロセス技術を確立した(図1、2)。これらの欠陥を高精度に検出可能とすべく開発した量産検査技術も活用して、大量生産における欠陥のバラつき要因を定量的に解明し、量産レベルで低欠陥を安定化させた。さらに、高温搬送と低熱容量化により昇降温時間を短縮させることで、生産性の向上も達成した。

3.開発技術の特徴と効果

表面欠陥、BPDの顕著な低減によりデバイスの初期電気特性歩留まり、および長期信頼性が向上し、デバイスの低コスト化と、車載や電鉄で要求されるレベルの高い信頼性構築に大きく貢献した。各分野でのパワーデバイスにおけるSiCの採用を促し、EVにおける約10%の航続距離向上(電費改善)、電鉄における約40%の省エネなどの効果をもたらしてきた。すでに普及が進んでいるこれらの分野に加えて、より大容量の応用分野である電力制御機器への適用を通じ、電力インフラを高度化していくことも期待される。

|